| 1000 | m    | min.  | min | m | mani | 11 | 71 | HT. | TT |

|------|------|-------|-----|---|------|----|----|-----|----|

|      | ALL. | 111.3 | Ш.  | Ш | ш    | Ш  | L  | u.  | Ш  |

DCEL101

|          | <br>-              | - | <br>- |  |  |

|----------|--------------------|---|-------|--|--|

| Don No.  | <br>1              |   |       |  |  |

| Reg. No. |                    |   |       |  |  |

|          | <br>Landau Control |   |       |  |  |

I Semester B.Sc. Degree Examination, May/June- 2022

## ELECTRONICS

Electronic Devices & Circuits

(NEP 2020 Scheme)

VIJAYA COLLEGE Jayanagar IV Block Bangalore-550 011

Paper: ELE -CT1

Time: 21/2 Hours

Maximum Marks: 60

Instructions to Candidates:

Answer all the questions from Part -A, any FOUR questions from Part-B and any FOUR questions from Part -C

Answer all the questions of Part-A in any one page and to be answered only Note: once. In this Part, answering the same question multiple times will not be considered for Evaluation. PART-A

Answer All the Sub divisions 1.

$(12 \times 1 = 12)$

- The circuit whose properties are same in either direction is known as

- Unilateral circuit a)

- b) Bilateral circuit

- Irreversible circuit c)

- d) Reversible circuit

- For maximum transfer of power, internal resistance of the source should be

- equal to load resistance

- Less than load resistance

- Greater than load resistance c)

- None of the above d)

- Theoretical value of efficiency for a full Wave Rectifier is

- 40.6% a)

81.2% - b)

21.0% c)

- 1.21% d)

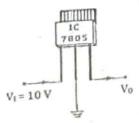

- Output voltage in the following circuit is

- 10 V

5V

-10V c)

-5 V d)

P.T.O.

- v) The transistor gets the name BJT as the conduction is

- a) Due to immobile ions.

- b) Due to only holes

- Due to both holes and electrons.

- d) Due to only electrons.

- vi) The correct relationship between the two current gains in BJT is

- a)  $\alpha = \beta/1 + \beta$

b)  $\alpha = 1 - \beta$

c)  $\alpha = \beta/1 - \beta$

- d)  $\alpha = \beta + 1$

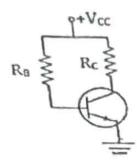

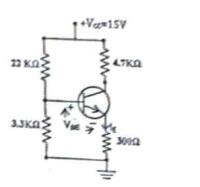

- vii) The biasing circuit shown in figure is

- a) Collector to base bias

- b) Voltage divider bias

c) Emitter bias

d) Fixed bias

- viii) Common collector amplifier is always used as

- a) Voltage amplifier

- b) Power amplifier

- c) Impedance matching amplifier

- d) audio amplifier

- ix) What is the input voltage of an amplifier with gain of 50 to generate 10V output?

- a) 1 V

b) 200mV

c) lmV

- d) 200V

- x) Which segments of a seven segment display need to be active in order to display a decimal digit 9?

- a) a, c, d, e, f

b) a, b, e, f, g

c) a, b, c, d, f,g

- d) c, d, e, f

- xi) The BCD code for decimal number 10 is

- a) 1000 0000

b) 0101 0000

c) 0000 1010

d) 0001 0000

|    | den had b                                                                    | III                                                                                                                                   | ID                                          | (3)                        |                      | DCE                                                        | L101                |  |

|----|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------|----------------------|------------------------------------------------------------|---------------------|--|

|    | xii)                                                                         |                                                                                                                                       | is a derived                                | logic gate.                |                      |                                                            |                     |  |

|    |                                                                              | a)<br>c)                                                                                                                              | OR gate<br>NOT gate                         | b)<br>d)                   | XOR gate<br>AND gate | LIBRARY<br>VIJAYA COLLI<br>Jayanagar IV B<br>Bangalota-560 | toe *               |  |

|    |                                                                              |                                                                                                                                       |                                             | PART - B                   |                      |                                                            |                     |  |

|    | Ans                                                                          |                                                                                                                                       | ny Four questions.                          |                            |                      |                                                            | $(4 \times 7 = 28)$ |  |

| 2. | a)                                                                           | <ul> <li>State Thevenin's theorem. With suitable circuit diagrams, explain the steps to<br/>Thevenise a resistive network.</li> </ul> |                                             |                            |                      |                                                            |                     |  |

|    | b)                                                                           | Drav                                                                                                                                  | w the input and outpu                       | t waveforms of H           | WR.                  |                                                            | (5+2)               |  |

| 3. | a) Drawthablant I'                                                           |                                                                                                                                       |                                             |                            |                      |                                                            |                     |  |

|    | b)                                                                           | Wha                                                                                                                                   | t are voltage multipli                      | iers?                      | 11.7                 | •                                                          | (5+2)               |  |

| 4. | a) Explain the input and output characteristic curves for a transistor in CE |                                                                                                                                       |                                             |                            |                      |                                                            | ode.                |  |

|    | b)                                                                           |                                                                                                                                       | blish the relation bet                      |                            |                      |                                                            | (5+2)               |  |

| 5. | With                                                                         | a cire                                                                                                                                | cuit diagram, explais<br>equency response.  |                            |                      | C coupled CE an                                            | plifier and (7)     |  |

| 6. | a)                                                                           | Expl<br>and I                                                                                                                         | ain with numerical e<br>Hexadecimal equival | xample, method<br>ent.     | to convert a de      | cimal number int                                           | o Binary            |  |

|    | b)                                                                           | Conv                                                                                                                                  | vert binary number 1                        | 11010101 <sub>0</sub> into | Gray code equ        | iivalent.                                                  | (5+2)               |  |

| 7. | a)                                                                           |                                                                                                                                       | and prove De Morg                           |                            |                      |                                                            |                     |  |

|    | b)                                                                           |                                                                                                                                       | y the universal prop                        |                            | by realizing A       | ND gate.                                                   | (5+2)               |  |

| 8. |                                                                              |                                                                                                                                       | y Four questions.                           | PART - C                   |                      | on's theorem.                                              | (4×5=20)<br>(5)     |  |

| 01 |                                                                              |                                                                                                                                       |                                             | L                          |                      |                                                            |                     |  |

9. Calculate efficiency and PIV of a FWR with an input voltage of 230V rms and load resistance of 100  $\Omega$ . Given  $r_d = 5\Omega$  and turns ratio 10:1. (5)

[P.T.O.

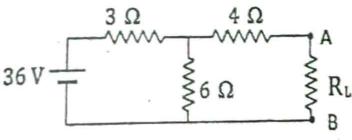

10. Calculate Iz (min) and Iz (max) in the circuit shown. Given: Vz=10V, Vin=36V and PZ = 500mW.

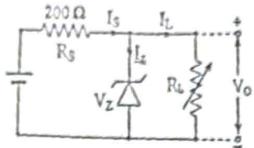

11. Draw the DC load line and mark the operating point for the biasing circuit shown in figure using Silicon transistor. Given  $\beta = 200$ .

Subtract 20H from 5EH using 2's complement method.

Add 10111<sub>(2)</sub> and 11010<sub>(2)</sub> express the result in decimal.

(3+2)

13. Simplify the Boolean expression  $Y = [A\overline{B}(C + AD) + \overline{AB}]C$  and realise using basic gates. (5)